Move Beyond SECDED: Meet DIMMGuard

Whether you manage a hyperscaler or just own a smartphone, DRAM errors can be equally frustrating – though their impact differs significantly. For personal devices, frequent refresh cycles drain battery life and disrupt your day. In large-scale AI training, silent data corruption can cost millions of dollars and…

Whether you manage a hyperscaler or just own a smartphone, DRAM errors can be equally frustrating – though their impact differs significantly. For personal devices, frequent refresh cycles drain battery life and disrupt your day. In large-scale AI training, silent data corruption can cost millions of dollars and waste weeks of progress. Life would be better without both.

In today’s data-driven world, reliability is critical. Whether you’re in hospital being treated with IoT devices, or just trying to SatNav your route there, we expect and rely on reliability. The growth in data dependence hasn’t been matched with growth in data error management.

But the battle against bit (and symbol) errors will soon be taking a big leap forward. Kandou is preparing to release a new suite of algorithms designed to detect and correct errors faster than ever. Enter DIMMGuard, Kandou’s low latency advanced error correcting codes. These new solutions will surpass the performance of traditional Single Error Correction, Double Error Detection (SECDED) systems that most have come to rely on, setting a new standard for error management in memory systems.

Offering Quad Error Correction / Quad Error Detection capability it will open up advanced performance and reliability to a range of verticals, like freeing up bandwidth in automotive and giving consumer laptops with LPDDR the kind of error correction upgrade normally reserved for server rooms.

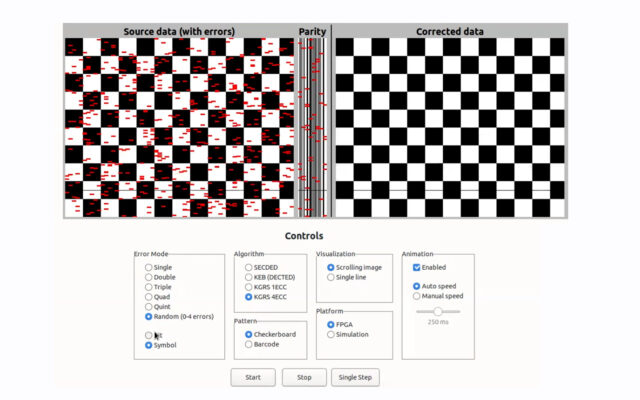

We’ll be unveiling DIMMGuard’s capabilities at OCP this October where you’ll be able to demo real time error correction and put each algorithm through its paces.

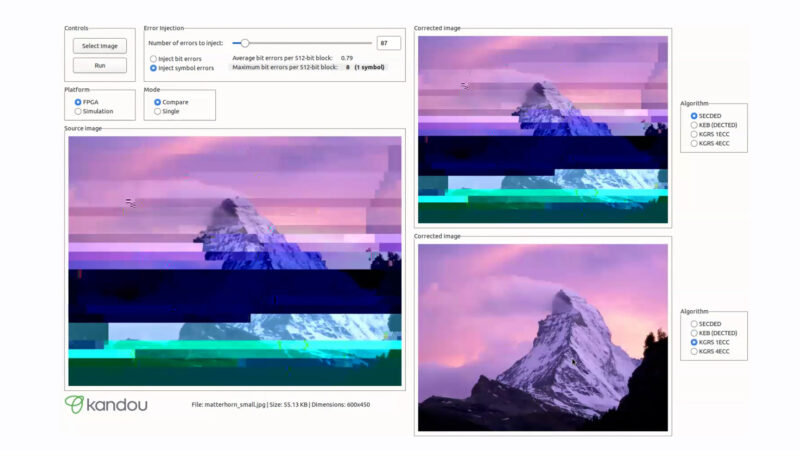

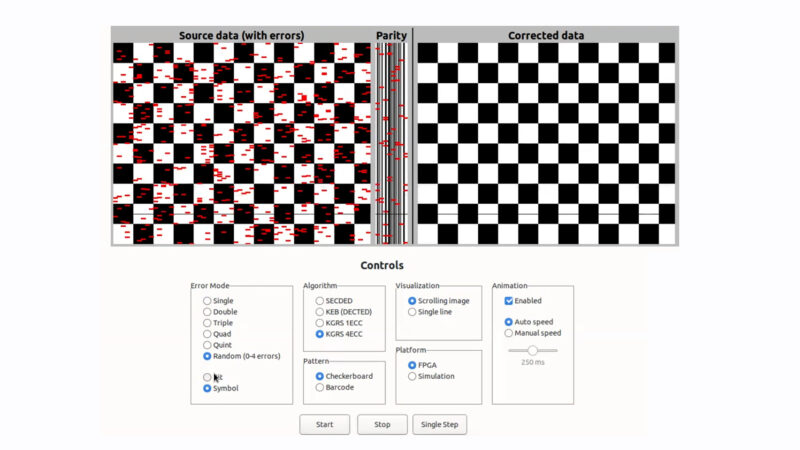

Here’s a little teaser of what you can expect to see…

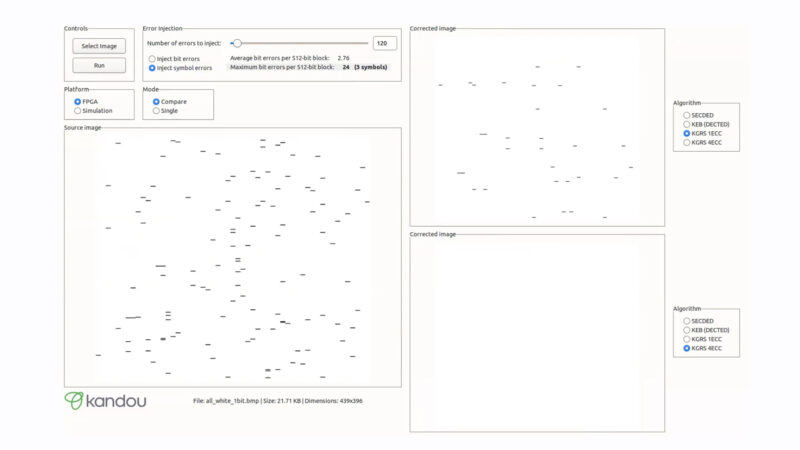

As you push the error creation harder you can toggle between bit and symbol errors at different scales, and watch each different algorithm fix them in the corrected image on the right – choosing from standard single bit error up to quadruple symbol error correction.

You can even perform in depth analysis of the error capabilities of each algorithm, by injecting a sequence of bit or symbol errors and really pushing DIMMGuard to its limits.

The cure for memory error headaches is coming. Watch out for updates, say hello and meet the team behind DIMMGuard at the Global Open Compute Project Summit in San Jose, California.